|

Yajun Ha |

|||

|

|

|||

|

|

Professor

School of Information Science and Technology ShanghaiTech University Pudong, Shanghai, China 201210

Phone: +86-021-20685371 Email: hayj@shanghaitech.edu.cn Office: Room 1D-401A, SIST Building |

||

|

|

|||

|

Research Interests |

|||

|

|

|||

|

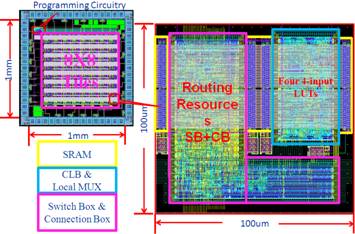

�� FPGA architectures, tools, and applications

|

|||

|

�� Ultra-low power circuits and systems

|

|||

|

�� Embedded system design and methodology for applications in hardware security, smart vehicles and machine learning

|

|||

|

|

|||

|

Biography |

|||

|

|

|||

|

He is currently a Professor at ShanghaiTech University, China. Before this, he was a Scientist and Co-Director, I2R-BYD Joint Lab at Institute for Infocomm Research, Singapore, and an Adjunct Associate Professor at the Department of Electrical & Computer Engineering, National University of Singapore. Between Mar 2004 and Dec 2013, he was an Assistant Professor with National University of Singapore. He received his Ph.D. degree from Katholieke Universiteit Leuven (KULeuven), Leuven, Belgium, in 2004 and worked at the same period as a researcher with the Inter-University MicroElectronics Center (IMEC), Leuven, Belgium.

He has served a number of positions in the professional communities. He serves as the Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS��PART I: Regular Papers (2016�C2017), the Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS��PART II: EXPRESS BRIEFS (2011�C2013), the Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS (2013�C2014), and the Journal of Low Power Electronics (since 2009). He has served as the General Co-Chair of ASP-DAC 2014; Program Co-Chair for FPT 2010 and FPT 2013; Chair of the Singapore Chapter of the IEEE Circuits and Systems (CAS) Society (2011 and 2012); Member of ASP-DAC Steering Committee; and Member of IEEE CAS VLSI and Applications Technical Committee. He has been the Program Committee Member for a number of well-known conferences in the fields of FPGAs and design tools, such as DAC, DATE, ASP-DAC, FPGA, FPL and FPT.

His research interests include reconfigurable computing, ultra-low power digital circuits and systems, and embedded system architecture and design tools for applications in hardware security, smart vehicles and machine learning. He has published around 100 internationally peer-reviewed journal/conference papers on these topics.

|

|||

|

|

|||

|

Current Opennings |

|||

|

|

|||

|

�� PhD student �� Research Assistant/Associate Professor �� Research Engineer

Please contact me for more details

|

|||

|

|

|||

|

Ongoing Projects |

|||

|

|

|||

|

1. Intelligent hardware design framework, Start-up Grant from ShanghaiTech University, Principal Investigator, RMB$5,000,000, 1/2017-1/2021.

|

|||

|

|

|

||

|

|

|||

|

2. Autonomous Electric Vehicle Technologies, Industry Grant from BYD, Co-Principal Investigator, S$36,000,000, 11/2013-10/2019.

|

|||

|

|

|

||

|

|

|||

|

Selected Publications |

|||

|

|

|||

|

1. M. Zhu, Y. Ha, C. Gu and L. Gao, ��An Optimized Logarithmic Converter with Equal Distribution of Relative Errors��, IEEE Transactions on Circuits and Systems II, Vol 63, Issue 9, pp848-852, Sep 2016. 2. A. Li, A. Kumar, Y. Ha and H. Corporaal, ��Correlation Ratio Based Volume Image Registration on GPUs��, Microprocessors and Microsystems (MICPRO), Vol 39, Issue 8, pp998-1011, Nov 2015. 3. G. Jiang, J. Wu, Y. Ha, Y. Wang and J. Sun, ��Reconfiguring Three-dimensional Processor Arrays for Fault-tolerance: Hardness and Heuristic Algorithms��, IEEE Transactions on Computers, Vol 64, Issue 10, pp2926-2939, Oct 2015. 4. W. Zhao, Y. Ha and A. Massimo, ��Novel Self Body-Biasing and Statistical Design for Near-Threshold Circuits with Ultra Energy-Efficient AES as Case Study��, IEEE Transactions on VLSI Systems, Vol 23, Issue 8, pp1390-1401, Aug 2015. 5. W. Zhao, A. Alvarez and Y. Ha, ��A 65-nm 25.1-ns 30.7-fJ Robust Subthreshold Level Shifter with Wide Conversion Range��, IEEE Transactions on Circuits and Systems II, Vol 62, Issue 7, pp671-675, July 2015.

For more publications, please see my CV. |

|||