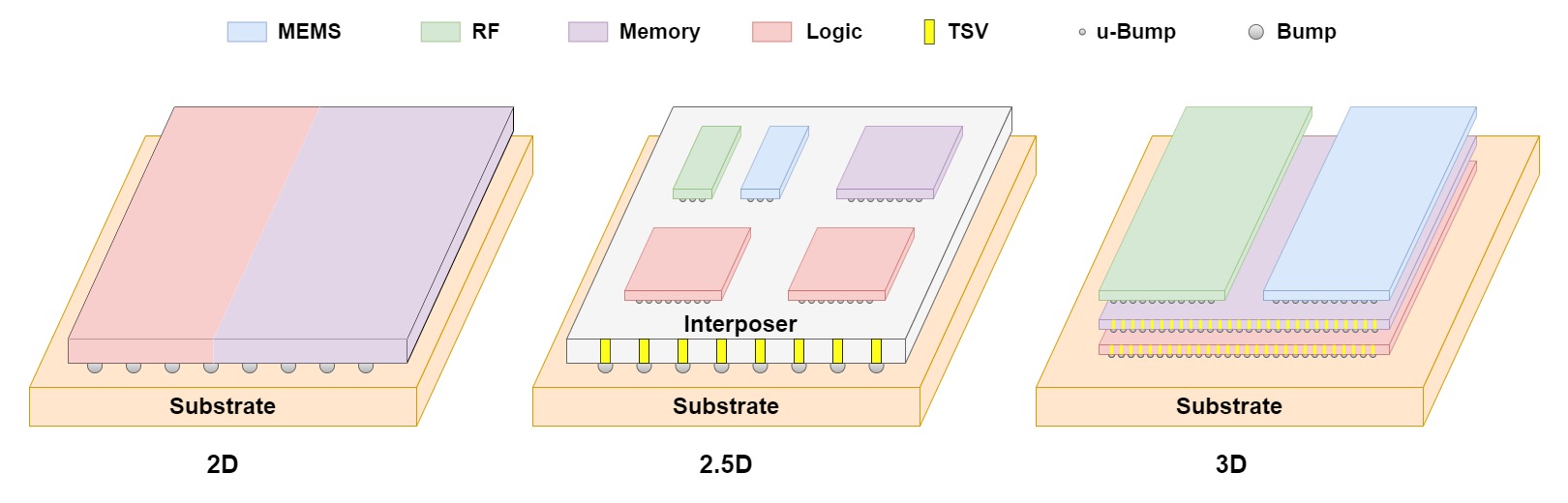

Project #1: EDA for 2.5D and 3D Circuits

Goals: Three Dimensional Integrated Circuit (3D-IC) can achieve high

integration density and fast intra-die connection by stacking

the dies vertically in one chip package with the help of the

Through Silicon Vias (TSVs). Besides, pioneering companies like

AMD are moving towards 2.5D integration for cost incentive –

they disintegrate the traditional monolithic single chip into

multiple smaller chiplets, and then implement the interconnects

among the chiplets by interposers at the package. The EDA

solutions for both 3D and 2.5D are not mature yet. Thus in this

project, we are interested in developing the techniques and

tools for 2.5D and 3D circuits.

Selected Publications

-

1. Jindong Zhou, Yuyang Chen, Youliang Jing and Pingqiang Zhou,

"The Study of

TSV-Induced and Strained Silicon-Enhanced Stress in 3D-ICs," Integration, the VLSI Journal, Vol. 88, pp. 196-202, January 2023.

-

2. Wei Gao, Zhiliang Qian, and

Pingqiang Zhou, "Reliability- and

Performance-Driven Mapping for Regular 3D NoCs Using A

Novel Latency Model and Simulated Allocation,"

Integration, the VLSI Journal, Vol. 65, pp. 351-361,

March 2019.

-

3. Pingqiang Zhou, Ping-Hung Yuh and Sachin S. Sapatnekar, "Application-Specific 3D Network-on-Chip

Design Using Simulated Allocation," Asia-South Pacific Design Automation Conference (ASP-DAC),

pp. 517-522, 2010. (Nominated for Best Paper Award).

-

4. Pingqiang Zhou, Karthikk Sridharan and Sachin S. Sapatnekar, "Congestion-Aware Power Grid Optimization for

3D Circuits Using MIM and CMOS Decoupling Capacitors," Asia-South

Pacific Design Automation Conference (ASP-DAC), pp. 179-184, 2009.

-

5. Pingqiang Zhou, Karthikk Sridharan and Sachin S. Sapatnekar, "Power Grid Optimization in 3D Circuits

Using MIM and CMOS Decoupling Capacitors," IEEE Design & Test,

Vol. 26, No. 5, pp. 15-25, 2009.

-

6. Pingqiang Zhou, Yuchun Ma, Zhouyuan Li, Robert P. Dick, Li Shang, Hai Zhou,

Xianlong Hong and Qiang Zhou, "3D-STAF:

Scalable Temperature and Leakage Aware Floorplanning for Three-dimensional

Integrated Circuits," IEEE/ACM International Conference on Computer-Aided

Design (ICCAD), pp. 590-597, 2007.

Project #2: AI for IC

Goals: AI is a promising and powerful agent for IC design. Starting from 2014,

our group has been developing AI techniques for data-driven IC design,

ranging from device modeling for a single transistor, to the automatic

design of analog ICs, up to the design challenges of communication, power

and signal integrity associated with a complete processor chip.

Device Modeling:

Selected Publications

-

1. Huifan Zhang, Youliang Jing and Pingqiang Zhou,"Machine

Learning-Based Device Modeling and Performance Optimization for FinFETs,"

IEEE Transactions on Circuits and Systems II: Express Briefs (TCAS-II), Vol. 70, No. 4, pp. 1585-1589, April 2023.

-

2. Youliang Jing,

Jindong Zhou and Pingqiang Zhou, "Parasitic

Capacitance Modeling of Si-Bulk FinFET-Based pMOS," IEEE Transactions on

Electron Devices (TED), Vol. 68, No. 10, pp. 4819-4825, October 2021.

Analog Circuits:

Selected Publications

-

1. Hongjian Zhou, Yaguang Li, Xin Xiong and Pingqiang Zhou, "A

Transferable GNN-based Multi-Corner Performance Variability Modeling for Analog ICs,"

IEEE Asia and South Pacific Design Automation Conference, pp. 411-416, 2024. (Nominated for Best Paper Award).

NoC (Chip Level):

Selected Publications

-

1. Yang Li and Pingqiang Zhou, "Fast

and Accurate NoC Latency Estimation for Application-Specific Traffics Via Machine Learning,"

IEEE Transactions on Circuits and Systems II: Express Briefs (TCAS-II), Vol. 70, No. 9, pp. 3569-3573, September 2023.

Power and Signal Integrity (Chip Level):

Selected Publications

-

1. Yuan Li and Pingqiang Zhou, "Full-Chip Voltage Prediction via Graph Attention Based Neural Networks,"

IEEE International Conference on ASIC (ASICON), 2023. (Invited).

-

2. Yaguang Li, Cheng Zhuo and Pingqiang Zhou,

"A Cross-Layer Framework for Temporal Power and Supply

Noise Prediction," IEEE Transactions on

Computer-Aided Design of Integrated Circuits and

Systems (TCAD), Vol. 38, No. 10, pp. 1914-1927, October 2019.

-

3. Yaguang Li, Cheng Zhuo and Pingqiang Zhou, "A

System-Level Framework for Online Power and Supply Noise Prediction in

Processor Chips," ACM/EDAC/IEEE Design Automation Conference (DAC), 2018. (Poster session)

-

4. Xiaochen Liu, Shupeng Sun, Xin Li, Haifeng Qian and Pingqiang Zhou, "Machine

Learning for Noise Sensor Placement and Full-Chip

Voltage Emergency Detection," IEEE Transactions on

Computer-Aided Design of Integrated Circuits and

Systems (TCAD), Vol. 36, No. 3, pp. 421-434, March 2017.

-

5. Xiaochen Liu, Shupeng Sun, Pingqiang Zhou, Xin Li and Haifeng Qian,

"A Statistical

Methodology for Noise Sensor Placement and Full-Chip Voltage Map

Generation," ACM/EDAC/IEEE Design

Automation Conference (DAC), pp. 1-6, 2015.

Project #3: Customized IC for AI (and its Applications)

Goals: Compared to GPUs and CPUs, customized AI accelerators are more

energy-efficient and are more suitable for resource-bounded applications.

In this project, we explore the design of AI accelerators in the context

of emerging devices (like memristor), new neural network (like spiking neural

network) and new applications (such as neural rendering) .

General AI Accelerator:

Selected Publications

-

1. Yuanchen Qu, Yu Ma and Pingqiang Zhou,

"A Speed- and Energy-Driven Holistic Training Framework for Sparse CNN Accelerators,"

Design, Automation and Test in Europe Conference (DATE), pp. 1-6, 2023. (Nominated for Best Paper Award).

-

2. Wei Gao and Pingqiang Zhou, "Customized

High Performance and Energy Efficient Communication

Networks for AI Chips," IEEE Access, Vol. 7, pp.

69434-69446, May 2019.

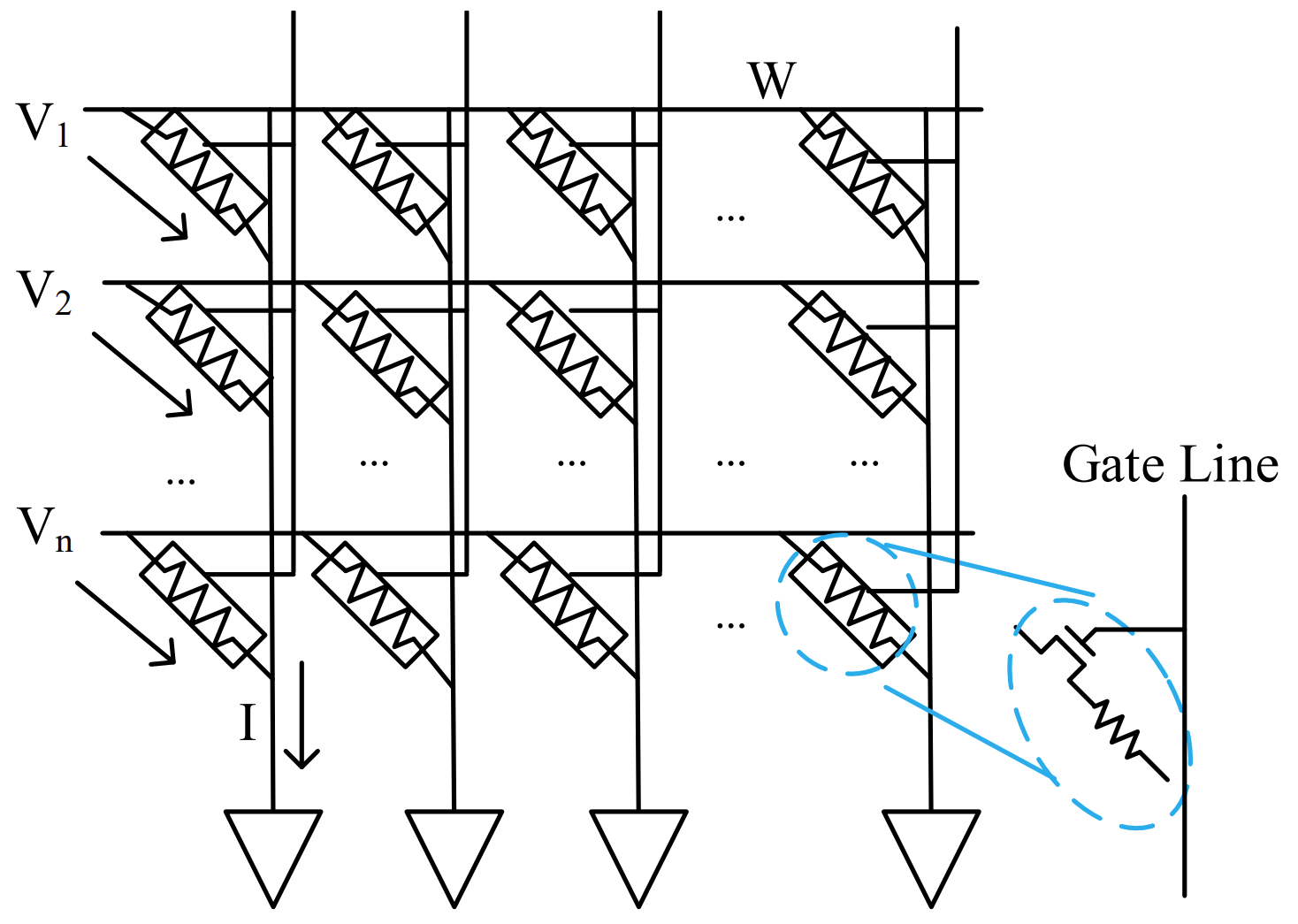

RRAM-based AI accelerator:

Selected Publications

-

1. Yu Ma, Linfeng Zheng∗ and Pingqiang Zhou,

"A Mapping

Method Tolerating SAF and Variation for Memristor Crossbar Array Based Neural Network Inference on Edge

Devices," ACM Journal on Emerging Technologies in Computing Systems (JETC), Vol. 19, No. 2, Article 15, pp. 1-21, May 2023.

-

2. Chengrui Zhang, Yu Ma and Pingqiang Zhou,

"Thermal-Aware Layout

Optimization and Mapping Methods for Resistive Neuromorphic Engines,"

IEEE Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 50-55, 2022.

-

3. Yu Ma, Chengrui Zhang and Pingqiang Zhou,

"Efficient

Techniques for Extending Service Time for Memristor-based Neural Networks,"

IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), pp. 81-84, 2021., pp. 50-55, 2022.

-

4. Yu Ma, Linfeng Zheng and Pingqiang Zhou,

"Tolerating Stuck-at Fault and Variation in Resistive Edge Inference Engine via Weight Mapping,"

Great Lakes Symposium on VLSI (GLSVLSI), pp. 313-318, 2021.

-

5. Yu Ma and Pingqiang Zhou, "Efficient Techniques for Training the Memristor-based Spiking Neural Networks Targeting Better Speed, Energy and Lifetime," IEEE

Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 390-395, 2021.

-

6. Chenguang Zhang and Pingqiang Zhou,

"A Quantized Training Framework for Robust and Accurate ReRAM-based Neural Network Accelerators," IEEE

Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 43-48, 2021.

Neural Rendering:

Selected Publications

-

1. Haochuan Wan, Linjie Ma, Antong Li, Pingqiang Zhou, Jingyi Yu, and Xin Lou, "Zerotetris: A spacial features similarity-based

sparse MLP engine for neural volume rendering," ACM/EDAC/IEEE Design Automation Conference (DAC), 2024. (To appear).

-

2. Zhechen Yuan, Binzhe Yuan, Yuhan Gu, Yueyang Zheng, Yunxiang He, Xuexin Wang, Chaolin Rao, Pingqiang Zhou, Jingyi Yu,

and Xin Lou, "A 0.59J/pixel High-throughput Energy-efficient Neural Volume Rendering Accelerator on

FPGA," IEEE Custom Integrated Circuits Conference (CICC), 2024. (To appear).

-

3. Kangjie Long, Chaolin Rao, Yunxiang He, Zhechen Yuan, Pingqiang Zhou, Jingyi Yu and Xin Lou,

"Analysis

and Design of Precision-Scalable Computation Array for Efficient Neural Radiance Field Rendering," IEEE Transactions on

Circuits and Systems I: Regular Papers (TCAS-I), Vol. 70, No. 11, pp. 4260-4270, November 2023.

-

4. Chaolin Rao, Qing Wu, Pingqiang Zhou, Jingyi Yu, Yuyao Zhang and Xin Lou,

"An

Energy-efficient Accelerator for Medical Image Reconstruction from Implicit Neural

Representation," IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I), Vol. 70, No. 4, pp. 1625-1638, April 2023.

-

5. Chaolin Rao, Huangjie Yu, Haochuan Wan, Jindong Zhou, Yueyang Zheng, Minye Wu, Yu Ma, Anpei Chen, Binzhe Yuan, Pingqiang Zhou, Xin Lou and Jingyi Yu,

"ICARUS:

A Specialized Architecture for Neural Radiance Fields Rendering," ACM Transactions on Graphics (TOG), Vol. 41, No. 6, pp. 1–14, December 2022.

-

6. Chaolin Rao, Huangjie Yu, Haochuan Wan, Jindong Zhou, Yueyang Zheng,

Yu Ma, Anpei Chen, Minye Wu, Binzhe Yuan, Pingqiang Zhou, Xin Lou and Jingyi Yu,

"ICARUS:

A Specialized Architecture for Neural Radiance Field Rendering,"

SIGGRAPH Asia, 2022.

-

7. Haochuan Wan, Chaolin Rao, Yueyang Zheng, Pingqiang Zhou and Xin Lou,

"A

Systolic Array with Activation Stationary Dataflow for Deep Fully-Connected Networks,"

IEEE 5th International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2023.

-

8. Haochuan Wan, Chaolin Rao, Yueyang Zheng, Pingqiang Zhou, Jingyi Yu and Xin Lou,

"SME:

A Systolic Multiply-accumulate Engine for MLP-based Neural Network,"

IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), pp. 270-274, 2022.

-

9. Chaolin Rao, Yueyang Zheng, Haochuan Wan, Pingqiang Zhou, Jingyi Yu and Xin Lou,

"An

Energy Efficient Precision Scalable Computation Array for Neural Radiance Field Accelerator,"

IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), pp. 260-264, 2022. (Nominated for Best Paper Award).

-

10. Yueyang Zheng, Chaolin Rao, Haochuan Wan, Yuliang Zhou, Pingqiang Zhou, Jingyi Yu and Xin Lou,

"An RRAM-based Neural Radiance Field Processor,"

IEEE International System-on-Chip Conference (SOCC), pp. 1-5, 2022.

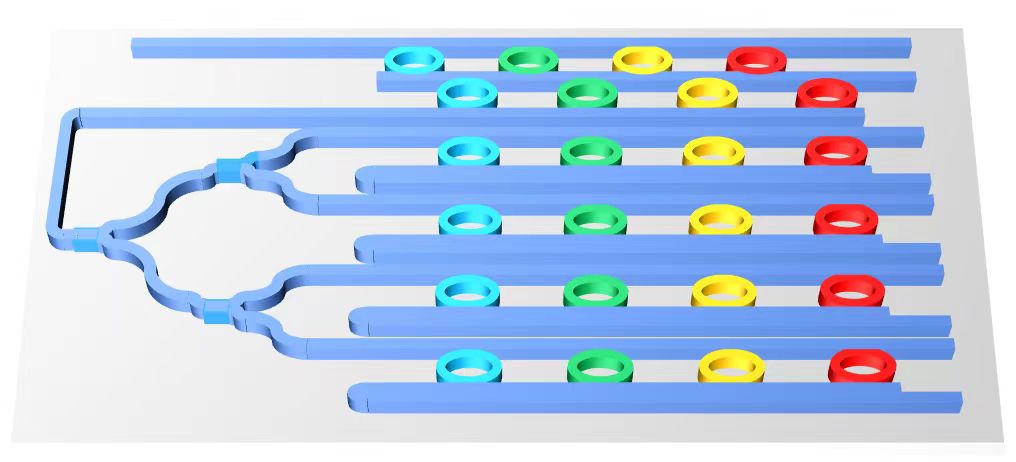

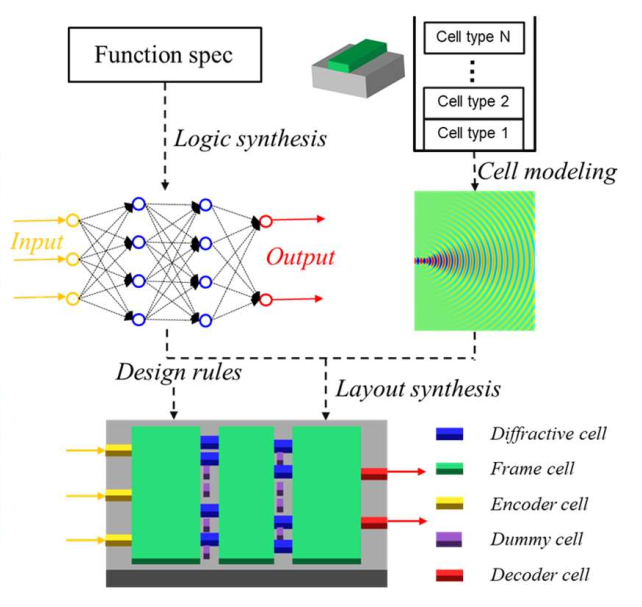

Project #4: Design and EDA of On-Chip Optical Neural Networks

Goals: Optical computing has been proposed to realize an accelerator of AI with high

speed and energy efficiency. On-chip Optical Neural Network (ONN) has exhibited

great potential due to the compatibility with the mature silicon process.

MZI-based ONN and diffractive ONN are two common approaches to realize on-chip ONN.

The goal of this project is to explore novel design and CAD techniques for on-chip

ONN considering the trade-offs among the footprint, optical loss and accuracy.

The overall system structure of the designed on-chip microring ONN array

Illustration of DONN chip design flow

The illustration of DONN handwritten digit classifier

Project #5: Security of Hardware and AI

Goals: The security of data processing in IC has always been a major concern in circuit design. New hardware

architectures or platforms proposed in recent years bring new security challenges, especially in the form of

side channel attacks (SCAs). For example, the data in cloud FPGA servers for multi-tenants may suffer from leakage.

Besides, in advanced packaging technologies like 3D integration, the information may leak through power side

channels in complex power distribution networks (PDNs). On the other hand, although AI techniques have been widely

used in variety of fields with great success, they are vulnerable to security issues. For example, adversarial

examples (artificial perturbations added to the clean image, usually imperceptible to human eyes), may mislead a

deep learning model. In this project, we aim to develop novel attack and defense mechanisms for IC and AI.

Selected Publications

-

1. Jinxin Dong and Pingqiang Zhou,

"Detecting

adversarial examples utilizing pixel value diversity," ACM Transactions on Design Automation of Electronic Systems (TODAES), Vol. 29, No. 3, Article 41, pp. 1–12, March 2024.

-

2. Yankun Zhu, Jindong Zhou and Pingqiang Zhou,

"Exploring

Remote Power Attacks Targeting Parallel Data Encryption On Multi-Tenant FPGAs,"

Great Lakes Symposium on VLSI (GLSVLSI), pp.57-62, 2023.

-

3. Yuan Liu, Jinxin Dong and Pingqiang Zhou,

"Defending against Adversarial Attacks in Deep Learning

with Robust Auxiliary Classifiers Utilizing Bit-Plane Slicing," ACM

Journal on Emerging Technologies in Computing Systems (JETC), Vol. 18, No. 3, Article 61, pp. 1-17, August 2022.

-

4. Jinxin Dong and Pingqiang Zhou,

"Detecting Adversarial Examples Utilizing Pixel Value Diversity,"

Asian Hardware Oriented Security and Trust Symposium (AsianHOST), pp. 1-6, 2021. (Nominated for Best Paper Award).

-

5. Yuan Liu and Pingqiang Zhou,

"Defending Against Adversarial Attacks in Deep Learning

with Robust Auxiliary Classifiers Utilizing Bit Plane Slicing," IEEE

Asian Hardware Oriented Security and Trust Symposium (AsianHOST), pp. 1-4, 2020.

-

6. Yajun

Yang, Zhang Chen, Yuan Liu, Tsung-Yi Ho, Yier Jin and Pingqiang

Zhou, "How

Secure is Split Manufacturing in Preventing Hardware Trojan?," ACM Transactions on Design Automation of Electronic Systems (TODAES),

Vol. 25, No. 2, Article 20, pp. 1-23, March 2020.

-

7. Zhang Chen, Pingqiang Zhou, Tsung-Yi Ho and Yier Jin,

"How

Secure is Split Manufacturing in Preventing Hardware Trojan?," IEEE

Asian Hardware Oriented Security and Trust Symposium (AsianHOST), pp. 1-6, 2016.