Research Projects Completed at ShanghaiTech University

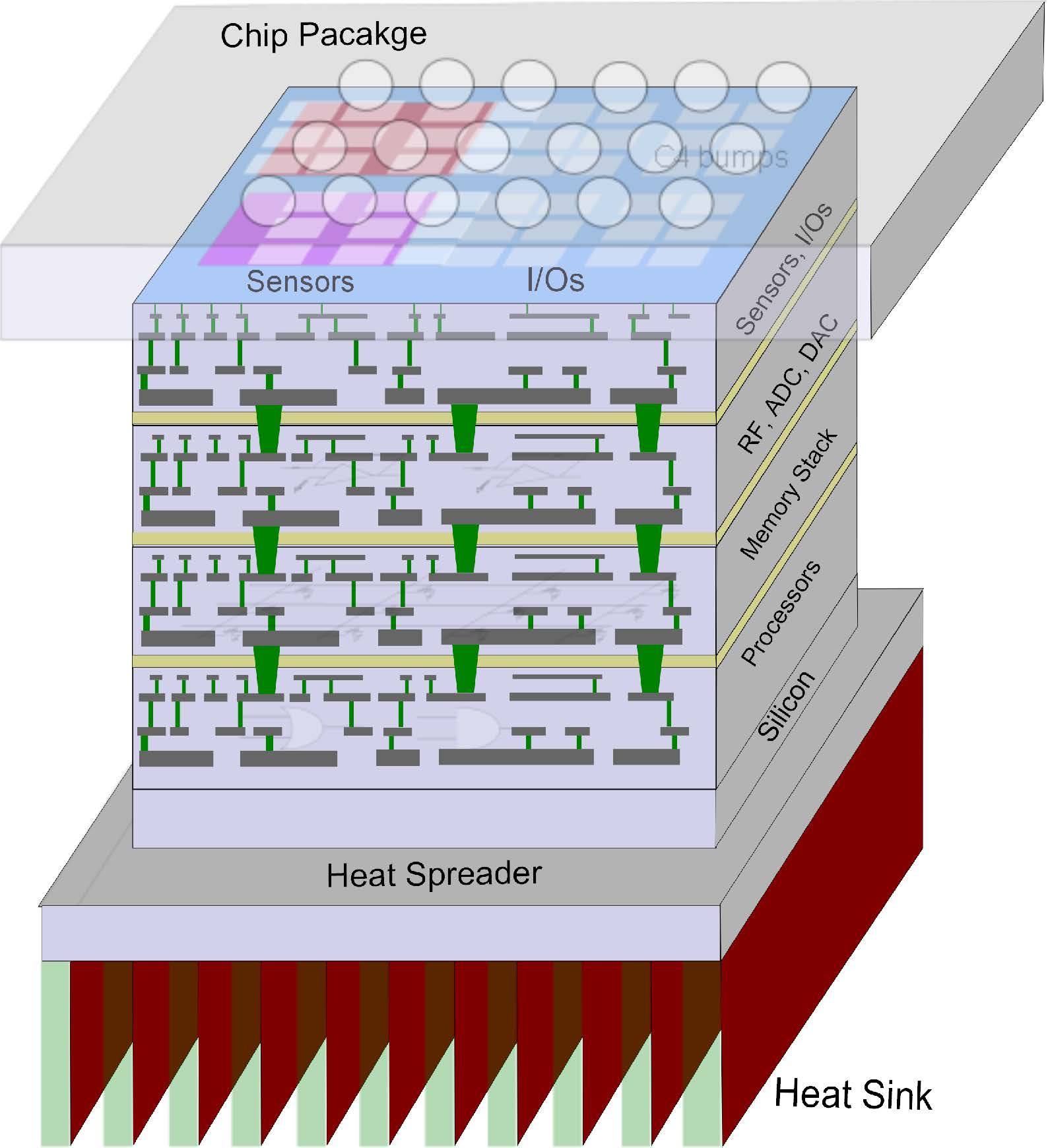

Goals: Three Dimensional Integrated Circuit (3D-IC) can archieve high integration density and fast intra-die connection by stacking the dies vertically in one chip package with the help of the Through Silicon Via (TSV). However, the manufacturing process of TSV will induce thermal stress in the die. The project firstly studies the stress distributions in the whole die. Also, other stress sources in 3D-IC like package componets, strained-Si technology and the Shallow Trench Isolation (STI) will be taken into consideration. Then how the stress influences the transistors as well as the circuits performances are researched.

Members: Youliang Jing, Jindong Zhou, Yuyang Chen

Related publications:

- 1. Jindong Zhou*, Yuyang Chen*, Youliang Jing and Pingqiang Zhou, "The Study of TSV-Induced and Strained Silicon-Enhanced Stress in 3D-ICs," Integration, the VLSI Journal, Vol. 88, pp. 196-202, January 2023.

- 2. Jindong Zhou∗, Youliang Jing and Pingqiang Zhou, "The Study of TSV-Induced and Strained Silicon-Enhanced Stress in 3D-IC," China Semiconductor Technology International Conference, pp. 1-3, 2021.

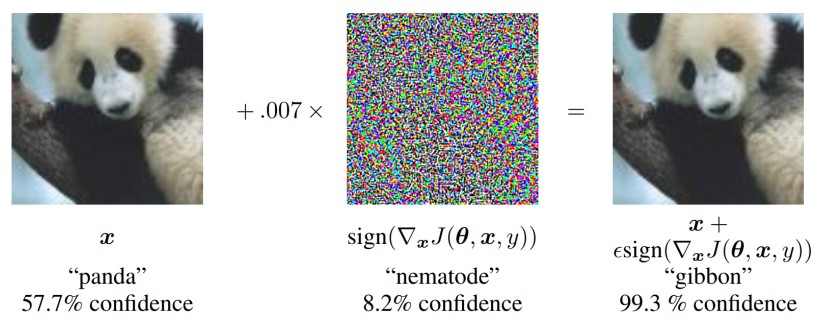

Goals: Adversarial examples have greatly threatened neural networks, and the application of neural networks has also been severely restricted. In this project, we study the amplitude characteristics of adversarial perturbations, and defend against adversarial examples based on the image's bit plane.

Members: Yuan Liu, Jinxin Dong

Related publications:

- 1. Yuan Liu*, Jinxin Dong* and Pingqiang Zhou, "Defending against Adversarial Attacks in Deep Learning with Robust Auxiliary Classifiers Utilizing Bit-Plane Slicing," ACM Journal on Emerging Technologies in Computing Systems, Vol. 18, No. 3, Article 61, pp. 1-17, July 2022.

- 2. Jinxin Dong* and Pingqiang Zhou, "Detecting Adversarial Examples Utilizing Pixel Value Diversity," Asian Hardware Oriented Security and Trust Symposium, pp. 1-6, 2021. (Best Paper Award Nomination)

- 3. Yuan Liu* and Pingqiang Zhou, "Defending Against Adversarial Attacks in Deep Learning with Robust Auxiliary Classifiers Utilizing Bit Plane Slicing," IEEE Asian Hardware Oriented Security and Trust Symposium, pp. 1-4, 2020.

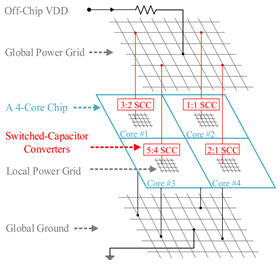

Goals: DVFS is one of the most effective techniques to reduce power consumption in multicore chips. The variations in the power demands over all the cores in chip can be best met if DVFS is supported by providing multiple levels of Vdd supplies from on-chip voltage regulators (DC-DC converters) that are essential components of the power delivery network. This project studies the design and optimization of SC converters for DVFS in multicore power delivery system that may have multiple power/voltage domains.

Members: Leilei Wang, Lu Wang, Dejia Shang, Chengrui Zhang, Yuanchen Qu

Related publications:

- 1. Yuanchen Qu, Lu Wang, Qingfu Xu and Pingqiang Zhou, "Two-Stage Energy Efficiency Optimization of Switched-Capacitor Converters for IoT Systems," IEEE International Symposium on Circuits and Systems, pp. 3068-3072, 2022.

- 2. Yuanchen Qu* and Pingqiang Zhou, "An Improved Design of Hybrid Integrated Voltage Regulator Based on DLDO and SCVR," IEEE International Conference on Solid-State and Integrated Circuit Technology, pp. 1-3, 2020.

- 3. Chengrui Zhang* and Pingqiang Zhou, "Improved Hierarchical IR Drop Analysis in Homogeneous Circuits," IEEE International Conference on Solid-State and Integrated Circuit Technology, pp. 1-3, 2020.

- 4. Leilei Wang*, Lu Wang*, Cheng Zhuo and Pingqiang Zhou, "Early-Stage Planning of Switched-Capacitor Converters in a Heterogeneous Chip," IEEE Access, Vol. 8, pp. 85900-85911, April 2020.

- 5. Lu Wang*, Leilei Wang*, Dejia Shang*, Cheng Zhuo and Pingqiang Zhou, "Optimizing the Energy Efficiency of Power Supply in Heterogeneous Multicore Chips with Integrated Switched-Capacitor Converters," The Design, Automation, and Test in Europe Conference, pp. 836-841, 2019.

- 6. Leilei Wang∗ and Pingqiang Zhou, "An Improved Leakage-Driven Runtime Decap Modulation Algorithm for Microprocessors," China Semiconductor Technology International Conference, pp. 1-3, 2018.

- 7. Leilei Wang*, Cheng Zhuo and Pingqiang Zhou, "Run-time Demand Estimation and Modulation of On-Chip Decaps at System Level for Leakage Power Reduction in Multicore Chips," Integration, the VLSI Journal, Vol. 65, pp. 322-330, March 2019.

- 8. Leilei Wang∗ and Pingqiang Zhou, "Leakage Power Reduction in Multicore Chips via Online Decap Modulation," China Semiconductor Technology International Conference, pp. 1-3, 2016. (Best Student Paper Award Nomination)

- 9. Pingqiang Zhou, "Design and Optimization of On-Chip Voltage Regulators for High Performance Applications," IEEE International Conference on Solid-State and Integrated Circiut Technology, pp. 1-4, 2014. (Invited)

- 10. Pingqiang Zhou, Ayan Paul, Chris H. Kim and Sachin S. Sapatnekar, "Distributed On-Chip Switched-Capacitor DC-DC Converters Supporting DVFS in Multicore Systems," IEEE Transactions on Very Large Scale Integration Systems, Vol. 22, No. 9, pp. 1954-1967, September 2014.

- 11. Pingqiang Zhou, Vivek Mishra and Sachin S. Sapatnekar, "Placement Optimization of Power Supply Pads Based on Locality," The Design, Automation, and Test in Europe Conference, pp. 1655-1660, 2013.

Goals: In modern microprocessor and SoC designs, supply noise margin has been significantly reduced due to the continuously decreasing supply voltage level. On the other hand, with increasing current density, chips may see larger supply noise variations on various spots and from time to time. As a result, chip robustness and reliability are inevitably deteriorated with more frequent supply noise emergencies. In this project, we aims to build a cross-layer framework for spatial and temporal supply noise prediction, using machine learning and statistical methods.

Members: Xiaochen Liu, Yaguang Li, Hui Zhao, Linfeng Zheng

Related publications:

- 1. Linfeng Zheng, Hui Zhao, and Pingqiang Zhou, "An Input-Sensitive Dynamic Power Modeling Methodology for AI Chips in Black-Box Form," IEEE International Conference on Solid-State and Integrated Circuit Technology, 2020.(Invited)

- 2. Yaguang Li*, Cheng Zhuo and Pingqiang Zhou, "A Cross-Layer Framework for Temporal Power and Supply Noise Prediction," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 38, No. 10, pp. 1914-1927, October 2019.

- 3. Rusong Weng∗, Yaguang Li∗, Wei Gao∗, Leilei Wang∗, Xufeng Kou and Pingqiang Zhou, "Deep Learning for Spatial Supply Noise Estimation in a Processor Chip," IEEE International Conference on Solid-State and Integrated Circuit Technology, pp. 1-4, 2018.

- 4. Yaguang Li*, Cheng Zhuo and Pingqiang Zhou, "A System-Level Framework for Online Power and Supply Noise Prediction in Processor Chips," ACM/EDAC/IEEE Design Automation Conference, 2018. (Poster Session)

- 5. Yaguang Li*, Pingqiang Zhou, "An Outlier Detection Method and its Application to Multicore-Chip Power Estimation," IEEE International Conference on ASIC, pp. 460-463, 2017. (Invited)

- 6. Pingqiang Zhou, "Design and CAD of Noise Sensors for On-Die Supply Voltage Emergency Detection," IEEE International Conference on Solid-State and Integrated Circuit Technology, pp. 593-596, 2016. (Invited)

- 7. Xiaochen Liu*, Shupeng Sun, Xin Li, Haifeng Qian and Pingqiang Zhou, "Machine Learning for Noise Sensor Placement and Full-Chip Voltage Emergency Detection," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 36, No. 3, pp. 421-434, March 2017.

- 8. Xiaochen Liu*, Shupeng Sun, Pingqiang Zhou, Xin Li and Haifeng Qian, "A Statistical Methodology for Noise Sensor Placement and Full-Chip Voltage Map Generation," ACM/EDAC/IEEE Design Automation Conference, pp. 1-6, 2015.

Goals: With the trend of outsourcing fabrication, split manufacturing is regarded as a promising way to both acquire the high-end nodes in untrusted external foundries and protect the design from potential attackers. In this project, we study the security level of split manufacturing under various attacks. We also study the corresponding effective defense methods.

Members: Zhang Chen, Yajun Yang, Jun Wen

Related publications:

- 1. Zhang Chen*, Pingqiang Zhou, Tsung-Yi Ho and Yier Jin, "How Secure is Split Manufacturing in Preventing Hardware Trojan?," IEEE Asian Hardware Oriented Security and Trust Symposium, pp. 1-6, 2016.

- 2. Yajun Yang*, Zhang Chen*, Yuan Liu*, Tsung-Yi Ho, Yier Jin and Pingqiang Zhou, "How Secure is Split Manufacturing in Preventing Hardware Trojan?," ACM Transactions on Design Automation of Electronic Systems, Vol. 25, No. 2, Article 20, pp. 1-23, March 2020.

Research Projects Involved at University of Minnesota, Twin Cities and Tsinghua University

Reliable power delivery is being recognized as a major challenge in multicore processors due to unpredictable loads and large switching transients between cores. Supply levels are steadily falling with technology scaling which results in less voltage headroom, while the total current drawn by a chip is increasing, with sub-32nm technologies showing especially high leakage current levels. These trends lead to worsening on-chip power supply noise that can cause a circuit to fail to meet its specifications. Today, even in single-core chips, or chips with a small number of cores, the power delivery problem is already one of the hardest problems facing a designer. This issue becomes progressively worse for future multicore systems. The goal of this project is to develop concrete design and CAD techniques for novel on-chip power delivery in multicore processors.

Related publications:

- 1. Pingqiang Zhou, Vivek Mishra, and Sachin S. Sapatnekar, "Placement Optimization of Power Supply Pads Based on Locality," The Design, Automation, and Test in Europe Conference (DATE), pp. 1655-1660, 2013.

- 2. Pingqiang Zhou, Bongjin Kim, Wonho Choi, Chris H. Kim, and Sachin S. Sapatnekar, "Optimization of On-Chip Switched-Capacitor DC-DC Converters for High-Performance Applications," Proceedings of the IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pp. 263-270, 2012.

- 3. Pingqiang Zhou, Dong Jiao, Chris H. Kim, and Sachin S. Sapatnekar, "Exploration of On-Chip Switched-Capacitor DC-DC Converter for Multicore Processors Using a Distributed Power Delivery Network," Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), pp.1-4, 2011. >

Process scaling and the critical reality of stringent power and thermal budgets have driven the growth of multicore systems. Homogeneous multicores consist of arrays of similar cores on the same die, while heterogeneous platforms integrate cores with different capacities, functionalities, or even different instruction set architectures, onto a single die. It is essential to design the cores, the communication network, and the memory system with the goal of optimizing system-level performance. The physical layout and topology of a multicore platform is closely related to architectural decisions, and design of these platforms must incorporate the close interaction between these two. This project develops dedicated CAD solutions that closely couple layout and architectural decisions to build optimized multicore platforms in both 2D and 3D IC paradigms.

Related publications:

-

1. Jieming Yin, Pingqiang Zhou, Sachin S. Sapatnekar, and Antonia Zhai, "Energy-Efficient Time-Division Multiplexed Hybrid NoC for Heterogeneous Multicore Systems," Proceedings of the IEEE International Parallel and Distributed Processing Symposium (IPDPS), 2014.

-

2. Pingqiang Zhou, Ping-Hung Yuh, and Sachin S. Sapatnekar, "Optimized 3D Network-on-Chip Design Using Simulated Allocation," ACM Transactions on Design Automation of Electronic Systems (TODAES), Vol.17, No.2, pp.1-19, 2012.

- 3. Jieming Yin, Pingqiang Zhou, Anup P. Holey, Sachin S. Sapatnekar, and Antonia Zhai, "Energy Efficient Non-Minimal Path On-chip Interconnection Network for Heterogeneous Systems," Proceedings of the ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), pp.57-62, 2012.

-

4. Pingqiang Zhou, Jieming Yin, Antonia Zhai, and Sachin S. Sapatnekar, "NoC Design and Performance Optimization," SRC TECHCON, 2011.

-

5. Pingqiang Zhou, Jieming Yin, Antonia Zhai, and Sachin S. Sapatnekar, "NoC Frequency Scaling with Flexible-Pipeline Routers," Proceedings of the ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), pp.403-408, 2011.

-

6. Pingqiang Zhou, Ping-Hung Yuh, and Sachin S. Sapatnekar, "Application-Specific 3D Network-on-Chip Design Using Simulated Allocation," Proceedings of the Asia-South Pacific Design Automation Conference (ASPDAC), pp.517-522, 2010.

3D circuit technologies, with multiple tiers of active devices stacked on top of each other, represent a key approach to achieving increased levels of integration and performance. However, to reach their full potential, the technologies must overcome two significant limitations, related to on-chip thermal issue and reliable power delivery. Both issues can be illustrated through a simple back-of-the-envelope calculation: A ktier 3D chip that stacks k similar chips could use k times as much current as a single 2D chip of the same footprint. However, the packaging technology is not appreciably different; with a similar heat sink, the on-chip temperature on such a 3D chip is k times higher than the 2D chip, and with a similar number of pins in the package, the current per pin is k times higher than the 2D case. The above analysis operates under very coarse assumptions (for example, a smart 3D designer may not stack k layers with identical power levels), and a more nuanced approach is necessary for a more accurate analysis - but the eventual conclusions that thermal and power delivery issues are important in 3D - are inescapable. The goal of this project is to develop novel CAD techniques for thermal optimization and reliable power delivery in 3D circuits.

Related publications:

-

1. Pulkit Jain, Pingqiang Zhou, Chris H. Kim, and Sachin S. Sapatnekar, "Thermal and Power Delivery Challenges in 3D ICs," in Three-Dimensional Integrated Circuit Design: EDA, Design and Microarchitectures, Springer, Boston, MA, 2010. (Book chapter)

- 2. Yuchun Ma, Qiang Zhou, Pingqiang Zhou, and Xianlong Hong, "Thermal Impacts of Leakage Power in 2D/3D Floorplanning," Journal of Circuits, Systems, and Computers (JCSC), Vol.19, No.7, pp.1483-1495, 2010.

-

3. Pingqiang Zhou, Karthikk Sridharan, and Sachin S. Sapatnekar, "Power Grid Optimization in 3D Circuits Using MIM and CMOS Decoupling Capacitors," IEEE Design & Test (D&T), Vol.26, No.5, pp.15-25, 2009.

-

4. Pingqiang Zhou, Karthikk Sridharan, and Sachin S. Sapatnekar, "Congestion-Aware Power Grid Optimization for 3D Circuits Using MIM and CMOS Decoupling Capacitors," Proceedings of the Asia-South Pacific Design Automation Conference (ASPDAC), pp.179-184, 2009.

-

5. Pingqiang Zhou, Jie Gu, Pulkit Jain, Chris H. Kim, and Sachin S. Sapatnekar, "Reliable Power Delivery for 3D ICs," Sematech Workshop on Design and Test Challenges for 3D ICs, 2008.

-

6. Pingqiang Zhou, Yuchun Ma, Zhouyuan Li, Robert P. Dick, Li Shang, Hai Zhou, Xianlong Hong, and Qiang Zhou, "3D-STAF: Scalable Temperature and Leakage Aware Floorplanning for Three-dimensional Integrated Circuits," Proceedings of the IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pp.590-597, 2007.

-

7. Pingqiang Zhou, Yuchun Ma, Qiang Zhou, and Xianlong Hong, "Thermal Effects with Leakage Power Considered in 2D/3D Floorplanning," Proceedings of the IEEE International Conference on Computer-Aided Design and Computer Graphics (CAD&CG), pp.338-343, 2007.